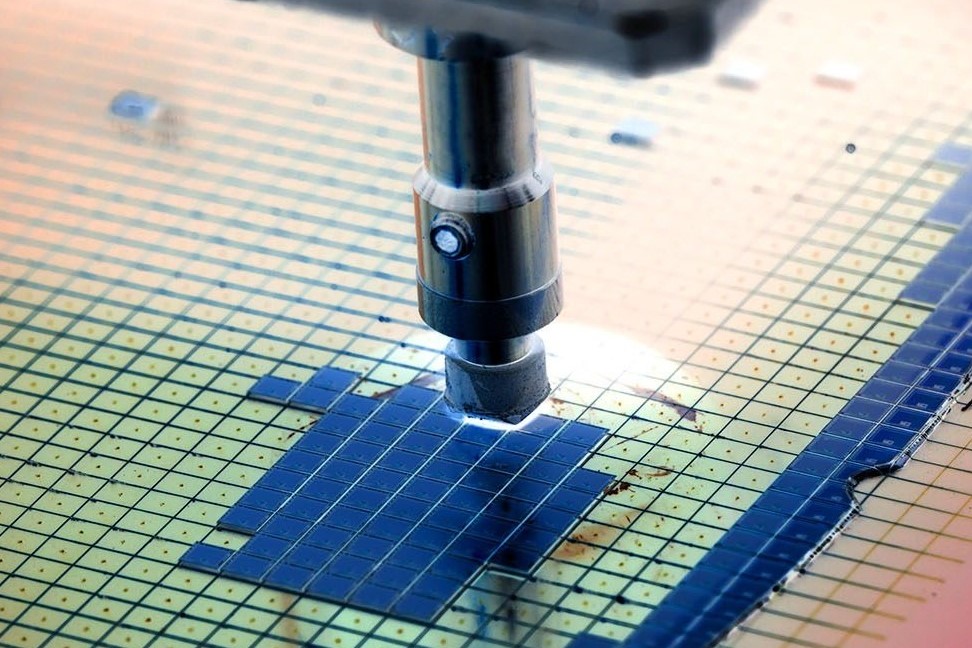

TSMC به یک موفقیت بزرگ در زمینه توسعه فرایند لیتوگرافی ۲ نانومتری دست پیدا کرده و از سال ۲۰۲۴ شاهد تولید انبوه پردازندهها با این فناوری خواهیم بود.

در گزارشی جدید و طبق اعلام منابع زنجیره تامین قطعات، فرایند لیتوگرافی ۲ نانومتری از معماری جدید «MBCFET» بجای معماری «FinFET» که در پردازندههای ۵ و ۳ نانومتری استفاده میشود، بهره میبرد. در این گزارش همچنین به این موضوع اشاره شده که TSMC به یک موفقیت بزرگ در زمینه توسعه این فناوری دست پیدا کرده که آن را جلوتر از رقبا مانند سامسونگ قرار میدهد. این کمپانی به دنبال تولید انبوه چنین تراشههایی در سال ۲۰۲۴ است.

مقامات TSMC به رسانهها اعلام کردهاند:

«ما امیدواریم که نرخ بازدهی تولید آزمایشی در نیمه دوم سال ۲۰۲۳ به ۹۰ درصد برسد که به ما در دریافت سفارشها از کمپانیهای بزرگ مانند اپل کمک میکند.»

در سال ۲۰۱۹ شرکت TSMC یک تیم تحقیق و توسعه برای یافتن راهی عملی برای توسعه فرایند لیتوگرافی ۲ نانومتری تشکیل داد. این تیم باید هزینه، سازگاری تجهیزات، کارایی فناوی و عملکرد و سایر عوامل را مدنظر قرار دهد.

یکی از نکات قابل توجه، استفاده معماری ۲ نانومتری از MBCFET مبتنی بر GAA است که محدودیتهای فیزیکی نشت جریان کنترلی ایجاد شده توسط فرایند FinFET را برطرف میکند.

در حالی که TSMC در حال کار روی پردازندههای ۲ نانومتری برای سال ۲۰۲۴ است، شروع به انجام تحقیقات پیرامون این فناوری کرده که شامل امکان تولید تراشههای ۱ نانومتری در آینده نزدیک میشود. این کمپانی تایوانی به دنبال گسترش کارخانه خود در مرکز تایوان برای فرایند لیتوگرافی ۲ نانومتری است که میتواند فاصله آن با رقبا مانند سامسونگ را بیش از پیش افزایش دهد.

TSMC امسال شروع به تولید پردازندههای ۵ نانومتری کرده که برای مثال میتوان به چیپ A14 Bionic مورد استفاده در آیپد ایر ۴ اشاره کرد. این کمپانی همچنین از تولید انبوه تراشههای ۳ نانومتری از سال ۲۰۲۲ خبر داده است.